### MASTER THESIS

OPTICAL FAULT INJECTION

ATTACKS IN SMART CARD

CHIPS AND AN EVALUATION

OF COUNTERMEASURES

AGAINST THEM

Nikolaos Athanasios Anagnostopoulos

FACULTY OF ELECTRICAL ENGINEERING, MATHEMATICS AND COMPUTER SCIENCE DEPARTMENT OF COMPUTER SCIENCE (EEMCS)

CHAIR OF SERVICES, CYBERSECURITY AND SAFETY (SCS)

prof. dr. F. E. Kargl prof. dr. ir. R. N. J. Veldhuis ir. J. T. M. H. Dielissen

DOCUMENT NUMBER EEMCS - 66014

# Nikolaos Athanasios Anagnostopoulos **Student number**: 1318055

# Optical fault injection attacks in smart card chips and an evaluation of countermeasures against them

### **Master Thesis**

Master Computer Science – EIT

Security & Privacy – specialisation Network Security

University of Twente

EIT ICT Labs Master School

2013-14

UNIVERSITEIT TWENTE.

### **Graduation advisors:**

Prof. Dr. F. E. Kargl (University of Twente)

Prof. Dr. Ir. R. N. J. Veldhuis (University of Twente)

Dr. J. Y. Petit (University of Twente)

Drs. J. Schut (University of Twente)

Ir. C. Groot (NXP)

Ir. J. T. M. H. Dielissen (NXP)

Ir. H. de Jong (NXP)

Dr. A. Jansman (NXP)

### **Graduation Committee:**

Prof. Dr. F. E. Kargl (University of Twente)

Prof. Dr. Ir. R. N. J. Veldhuis (University of Twente)

Ir. J. T. M. H. Dielissen (NXP)

### Acknowledgements

I would like to thank all those people who accepted me, put up with me and helped me both in my life and, in finishing my master studies and this thesis, including my parents, my friends, as well as my professors, colleagues and supervisors.

"Life is unfair, but you gotta make the best of whatever you have..."

- from "Malcolm in the Middle"

Την φανέλα μου φορώ με τον κίτρινο θεό...

### **Table of Contents**

| Abstract                                                                                                                             | i      |

|--------------------------------------------------------------------------------------------------------------------------------------|--------|

| Chapter 1:                                                                                                                           |        |

| Introduction – The importance of security in a smart card chip.                                                                      | 1      |

| Categories of attacks and attackers                                                                                                  |        |

| A novel attack: Optical fault injection                                                                                              |        |

| Current countermeasures.                                                                                                             |        |

| Problem statement.                                                                                                                   |        |

| Research questions.                                                                                                                  |        |

| Methodology                                                                                                                          |        |

| The relation between cost and security                                                                                               |        |

| Acceptable risk: a balance between cost and security                                                                                 |        |

| Chapter 2:                                                                                                                           |        |

| Background and related work – Optical fault injections                                                                               | and    |

| countermeasures against them                                                                                                         |        |

| Optical fault injection                                                                                                              |        |

| Specifics of the physical mechanism behind optical fault injection                                                                   | 0      |

|                                                                                                                                      | 7      |

|                                                                                                                                      | /<br>n |

| Probable targets and technical characteristics of optical fault injection attacks.                                                   |        |

| attacksTechnical characteristics of front side attacks                                                                               |        |

| Technical characteristics of backside attacks                                                                                        |        |

| A comparison between frontside and backside attacks.                                                                                 |        |

| Lasers as a means for optical fault injections                                                                                       |        |

| Continuous wave and pulsed lasers as means for optical fault injections                                                              |        |

| Two-photon absorption in silicon and its significance as a future attack                                                             |        |

| mechanism                                                                                                                            | 11     |

| The importance of the laser spot size in optical fault injections                                                                    | 12     |

| Light detectors as a countermeasure against optical fault injections                                                                 |        |

| Incompatibilities as a restraining factor.                                                                                           | 13     |

| Compatible devices.                                                                                                                  | 14     |

| A comparison of the compatible photodetectors and related potential                                                                  | 1.0    |

| improvements.                                                                                                                        |        |

| The cost of photodetectors in relation to the protection they provide  Potential problems regarding the operation of light detectors |        |

| Examining possible alternatives                                                                                                      |        |

| Physical alternative countermeasures                                                                                                 |        |

| Enhancing pre-existing structures.                                                                                                   |        |

| Potential logical countermeasures                                                                                                    |        |

| Final remarks                                                                       | 29       |

|-------------------------------------------------------------------------------------|----------|

| Chapter 3:                                                                          |          |

| The study and its results - A comparison and evaluation                             | ation of |

| countermeasures                                                                     | 30       |

| Physical countermeasures.                                                           | 31       |

| Selection of the design ideas to be explored in detail                              | 31       |

| Design and Simulation                                                               |          |

| Results                                                                             |          |

| Logical countermeasures                                                             |          |

| Parity checking designs                                                             |          |

| Modular redundancy elements                                                         |          |

| Autocorrection on a single register file                                            |          |

| General remarks on the designs                                                      |          |

| Results                                                                             |          |

| Additional remarks on the evaluated countermeasures                                 | 58       |

| Chapter 4:                                                                          |          |

| Future work proposals and final remarks and conclusions                             | 65       |

| Software                                                                            | 67       |

| Hardware                                                                            | 68       |

| Logic                                                                               | 70       |

| Final remarks and conclusions.                                                      |          |

| References                                                                          | _        |

| Appendix                                                                            |          |

| • Verilog code for standalone 32x16 register                                        |          |

| • Verilog code for a 32x16 register incorporating checksum                          |          |

| • Verilog code for a 32x16 register integrating CRC                                 |          |

| <ul> <li>Verilog code for a 32x16 register containing single parity bi</li> </ul>   | • •      |

| word                                                                                | -        |

| • Verilog code for a 32x16 register containing parity bits per                      | 1 1      |

|                                                                                     | App. 7   |

| <ul> <li>Verilog code for a 32x16 register incorporating Hamming code</li> </ul>    | 1 1      |

| (implementation A without autocorrection)                                           |          |

| <ul> <li>Verilog code for a 32x16 register containing Hamming code</li> </ul>       | • •      |

| (implementation B without autocorrection)                                           |          |

| • Verilog code for a 32x16 register with dual modular redundations.                 |          |

|                                                                                     | App. 15  |

| <ul> <li>Verilog code for a 32x16 register with triple modular redundant</li> </ul> |          |

| -                                                                                   |          |

|                                                                                     | rxpp. 1/ |

### **Abstract**

This document is a study of optical fault injection attacks and countermeasures against them, with particular emphasis on an evaluation and comprehensive comparison of the different methods, techniques, structures and implementations which can be used as countermeasures.

Initially, it is examined why this topic is significant, important and relevant for computer security, especially from the perspective of a relevant business firm, especially regarding financial issues, such as cost. Then we make a comprehensive and detailed introduction to optical fault injection attacks against smart card chips and the countermeasures employed against such attacks, including a review of the current solution of using light sensors as countermeasures and the potential shortcomings of this solution.

We continue by identifying and investigating other potential alternative countermeasures against optical fault induction attacks. We then proceed to make a full evaluation and comparison of them, including some of their different implementations, regarding the balance between the diverse costs required for their implementation in a smart card chip and the level of protection they would offer. Additionally, we also relate the results of this comparison to the results that the current solution provides.

We then go on to discuss what future work we have identified that it may be needed regarding this field. Different innovative approaches are discussed and the thesis concludes with some additional remarks regarding these proposals and some final conclusions drawn from the comparison between currently used and alternative countermeasures.

Keywords: optical, fault, injection, laser, countermeasures, evaluation, security, cost, risk

### Chapter 1: Introduction – The importance of security in a smart card chip

It is an undeniable fact that a large number of both online and offline transactions are conducted nowadays with the use of smart cards. [1] Most of these transactions make use of the security features found on the chips that these cards carry, such as encryption mechanisms and secret keys and codes. It is therefore crucial to protect these features from being compromised, in order to maintain the integrity, confidentiality and availability of the sensitive and/or confidential data stored in these smart cards.

Additionally, the increased usage of smart cards also introduces higher incentives for both culprits and researchers to discover and commence attacks against the integrated circuits of such cards, which also result in a raising demand for the integration of better and more efficient security features in such chips.

It is therefore, essential to assess how the addition of new security features to a chip may affect its development and production costs, and whether such costs may be justified by potential losses and damages that may otherwise occur. Moreover, apart from direct economic losses and costs, a hardware attack on the integrated circuits of smart cards can also cause serious harm to the relevant company's prestige and brand name.

Potential future clients will be quite unwilling to place their trust on a company that has failed to secure its current clients' private data and their online – or offline – transactions. Therefore, it seems extremely crucial for a company manufacturing chips for smart cards to place significant effort and resources on assuring their security, by strengthening any security measures that have already been implemented on them and developing further more adequate and efficient ways to reinforce their security.

It is also really important for manufacturers of chips for smart cards to continuously monitor the most recent developments in attacking such integrated circuits, because only in this way an adequate effort can be made towards providing sufficient countermeasures against the latest reported attacks. In general, because the development of a new chip usually takes at least a couple of years, it is inevitable that new ways of compromising the chip's security measures will be developed before the chip reaches the market. As this new information cannot be integrated in a chip's architecture, design and features, while this is already being developed, without considerable new cost, the original design of such an integrated circuit must already implement a substantial degree of novelty regarding its security features, which may be able to counter future attacks. [2]

### Categories of attacks and attackers

Attacks can be classified as invasive, semi-invasive or non-invasive depending on their degree of physical penetration of the chip.<sup>[3][4]</sup> Invasive attacks involve altering the chip's physical structure in some way, semi-invasive ones only entail removing the chip's packaging, while non-invasive ones do not physically alter the chip and its packaging.<sup>[4]</sup> Furthermore, attacks can be classified as active or passive.<sup>[5]</sup> Active attacks involve altering the chip's data, functions or structure, in order to cause leakage of data or damage the chip's availability or integrity, while passive attacks just observe the

chip's functions, data or structure, in order to identify possible leakages of secure or private data.<sup>[4]</sup> Finally, attacks may target not only the confidentiality of the data found in a secure chip, but also their integrity or availability.

Successful attacks on such chips may cause damages and losses of millions, or even billions, of euros.<sup>[1][6]</sup> It is, therefore, evident that there are high incentives both for culprits to develop such attacks and for secure chip manufacturers to try to counter them as effectively as possible. Apart from this, academic researchers also try to develop both theoretical and practical ways of attacking secure integrated circuits in an effort to push forward research on this field, while also gaining potential benefits regarding their careers.<sup>[3][2]</sup> Furthermore, intelligence agencies of different countries as well as competitors could have the motivation to stage an attack against integrated circuits that are used in secure transactions.<sup>[3]</sup> Finally, a certain category of people may try to successfully penetrate secure chips just to test their own skills and abilities.<sup>[2]</sup>

### A novel attack: Optical fault injection

A large number of different ways to attack secure chips have been developed over the years, as well as adequate countermeasures against such known attacks.<sup>[3]</sup> However, constantly new more innovative ways of attacking such integrated circuits are being developed and, in such a fast pace, that current development must take into account potential future attacks and come up with novel ideas, ways and means of protecting future chips against not only currently known attacks, but also potential future ones.<sup>[2]</sup>

Such a recently identified category of attacks on secure chips is optical fault injection. Fault injection, or perturbation, is the process of altering the chip's data, functions or structure in such a way as to cause faults, calculations being performed with false data values. Its aim is to circumvent, penetrate or disable the chip's security. [4] Optical fault injection tries to achieve this through the use of optical means, light from lasers or other sources which will cause the injection of faults in integrated circuits. This attack was based on the previously observed effects of ionising radiation on semiconductors. [7] Ionising radiation can cause semiconductor transistors to be turned on, potentially causing faults and errors in the operation of the overall circuit. [8] This effect was replicated with the use of intense light and could potentially lead in the leakage of sensitive information. [7]

### **Current countermeasures**

Several ways exist to deal with both ionising radiation and optical fault injection attacks. [8] However, the most commonly used countermeasures against optical fault injections are light detectors. Such light detectors can be light-sensitive semiconductor devices integrated in the rest of the circuit and developed on the surface of a silicon (Si) wafer along with the rest of the chip's die. Nevertheless, this solution may not always provide an adequate level of security, because of the limitations of such devices regarding their area of detection and their detection thresholds. Moreover, these devices can be pretty large and this may add significant production costs, because more area, and thus more materials, will be needed if they are integrated in a chip.

### **Problem statement**

In general, even though a novel attack method may currently be considered complex, expensive and time consuming, it will eventually become more accessible and less costly to perform. As this may

slowly be happening with optical fault injection attacks as well, it is really important to examine the different ways of performing such attacks and whether there any potential shortcomings in the current countermeasure employed, photodetectors.

Even if the current countermeasure employed against optical fault injections is completely adequate against them, we should try to come up with additional countermeasures, in order to avoid future evolutions of optical fault injections attacks outperforming the current security incorporated in the final product, the smart card chip. Such solutions may include both physical and logical ways of increasing the robustness of the chip's circuit against optical fault injection attacks, as well as detecting such attack attempts. Consequently, we should, of course, compare the benefits and costs of the current solution employed, light detectors, to the ones related to the proposed new countermeasures, taking into account the level of security required.

Determining the level of security that is required for a smart card chip seems to be a complex process that is dependent on the manufacturing company, the client and, to a lesser extent, on the current certification and accreditation requirements. Therefore, it may not be possible to fully decide if a particular countermeasure provides enough protection at an efficient cost, and therefore may be considered an adequate one or not, as this decision has to be taken by the different stakeholders. Additionally, we cannot exactly determine the actions that should be programmed to be taken in the event of a successful detection of an attack, as these have to be determined between the client and the manufacturer.

Nevertheless, we can try to assess the relation between the costs and the benefits for the current solution and compare it to other proposed ways of detecting and/or protecting against optical fault injection attacks, in order to determine a relevant comparison and evaluation between the different options available. It would therefore be essential to define the different agents of cost identified in the production of a security component incorporated in a smart card chip, and, therefore, also in the production of the chip itself. In addition to this, we also need to examine the potential protection such a component may offer, in our case against optical fault injections.

Furthermore, we would, of course, need to take a look on how optical fault injection attacks may be enhanced in the future, in order to also be ready, in the future, to determine adequate countermeasures against such evolved attacks. However, as we cannot predict the future, we also cannot use the protection a countermeasure may be offering against a potential future evolved attack as an objective criterion regarding its merits. It would be up to the different stakeholders involved in the secure smart card market sector to determine the validity of such concerns over evolved attacks and thus, the need for adequate countermeasures against them.

### **Research questions**

Having determined the problem that this thesis will address, we can now to define the following research questions based on this problem that we will try to answer:

- How do optical fault injections work? What is the physical mechanism behind them?

- What are the current countermeasures incorporated in smart card chips against optical fault injection attacks and how do they counter them?

- How adequate are such countermeasures and what are their potential shortcomings?

- Are there other countermeasures which could address these shortcomings?

- How do the different countermeasures compare to each other regarding cost and protection?

- Which factors may affect their effectiveness and cost efficiency?

- Can some countermeasures be considered optimal or potentially lead into (more) robust smart card chips against light attacks?

- Can we come up with a proposal for a better solution than the currently employed one?

### Methodology

In order to answer these research questions, the following methodology was used. Initially, we conducted a literature study on both the relevant background of the topic and the topic itself, in order to gain knowledge on the different mechanisms, methods and facts concerning both optical faults injection attacks and countermeasures against them.

We then conducted a more in-depth study on the reported effectiveness of current countermeasures and on different proposed countermeasures, as well as coming up with a number of potential countermeasure ideas of our own. Our ideas mainly consisted of different photodetector structures and other mechanisms which would prevent light from reaching the sensitive parts of the chip or would at least detect either light itself or the faults induced by it.

Following this, we examined the proposed countermeasures for their effectiveness, probable cost and general feasibility to be implemented and integrated in secure smart card chips. We also designed and simulated some of the more efficient countermeasures proposed and examined in detail their potential protection level against optical fault injections in relation to their cost in terms of area and power consumed.

We then came up with a set of criteria in order to determine how general categories of countermeasures performed against each other and which of the designed solutions could be considered more optimal. Finally, we suggest what seems to be the most optimal solution and suggested different topics on which future research needs to be conducted.

### The relation between cost and security

It is important to explain here why cost plays such a significant role in determining the efficiency of a solution in being actually implemented. It should be evident that any additional security feature integrated in a smart card chip will need to be extensively tested, as it regards applications which require a significantly high degree of security. Such a solution not only has to work efficiently, but also must be sufficiently robust itself against not only already known, but also potential future, attacks. Therefore, it requires an exhaustive amount of designing and testing both as a prototype, but also when manufactured in mass quantities.

Thus, although the integration of security measures in such chips is intentionally sought-after and inherently unavoidable, [9] it comes at a large cost. Inherent costs exist due to the research and development phase of such features, which include manpower and infrastructure costs, as well as costs for the design and implementation of their prototypes and, potentially, of the whole chip, as the chip may need to be significantly redesigned. Furthermore, significant costs may also occur

during the mass production of the chip, as the new features may increase the chip's area and thus raise the cost of the materials required for its production.

Moreover, the addition of security features may also introduce performance costs, related to the chip's computation time, delay costs, as well as power costs, due to the increased complexity of the new integrated circuit and the need to also provide enough power for the additional features. Additionally, the integration of such novel security features can also imply a rise in packaging and marketing costs and surely involves a significant rise in costs for testing, as the new features require unit testing on their own, integration testing towards the rest of the chip and a full system and acceptance testing for the new chip as a whole.

All in all, the overall costs for the research and development phase may rise well into the region of hundreds of millions of euros.<sup>[10]</sup> And, although it has been noted that the cost of research and development for semiconductor products exceeds that of most other high technology industries, the cost of a semiconductor fabrication plant is estimated to be at least a few billion euros, <sup>[12][13][14][15]</sup> which also makes the cost of using its services extremely high. It is for this reason that any changes required to be made in the manufacturing process also come at an extremely high cost.

Finally, it must be noted that the smart card security market sector is highly based on economies of scale and rather relies on incompatibilities to act as high barriers to enter it. Additionally, lock-in effects are being used by big companies in it in order to control a certain share of the market. Therefore, cost plays a significant role in every aspect of this market, as it can significantly affect the share of the market controlled.

### Acceptable risk: a balance between cost and security

It is really critical to note here that a balance exists between the levels of cost and provided security, defined through a level of *acceptable* risk. As it was quite early recognised that hardware can never become invulnerable to each and every kind of attack, [17] a level of risk is now always considered acceptable regarding security. Therefore, given the relation between cost and security, by defining a level of acceptable risk, a level of adequate protection is also defined, which leads to trying to achieve the lowest level of cost possible while maintaining that set level of security. Additionally, the level of acceptable risk is also dependent on the costs of performing a successful attack. If such costs are high, then the level of acceptable risk can also be high.

Cost is a critical factor for attacks targeted at secure hardware, because they quite often require the use of advanced equipment in a very specific way and expert knowledge, not only in the general field, but also about the very specific hardware to come under attack. Also, such attacks can far less often be automated in comparison to software attacks, thus their yield over time is much smaller. Moreover, as hardware attacks are more physical in their nature than software attacks, they often require a large number of integrated circuits of the same kind in order to be successful, which may generally be hard to obtain. In conclusion, this means that performing a hardware attack tends to have a high cost, which may not always be justified by its potential benefits and rewards for the attacker.

However, hardware attacks can cause damages or losses amounting to several millions of euros. Especially when chips integrated in bank cards are targeted, the losses may potentially be in the region of billions of euros. [1] It is therefore evident that depending on their uses and their potential clients, different smart card chips have very different levels of acceptable risk. Another important factor determining the level of acceptable risk is the number of smart cards that may be potentially

compromised by a single attack. If a specific attack which is not uncommon can give the attacker access to a large number of different cards, then, the acceptable risk will obviously be particularly low.

For example, NXP's MIFARE brand of smart cards had recently come under increased attack in an effort to identify potential ways to overcome its security features and gain access on confidential information stored on the cards. [18][19][20][21][22][23][24][25][26] Researchers have quite often succeeded in compromising the security of these smart cards. [18][19][20][23][24][26] The MIFARE company claims to possess "a confirmed market share of 77% in public transport", [27] which is equivalent to at least 1 billion of its cards being used for secure online transactions related to transportation. [23] This means that if the techniques demonstrated by these researchers were to be employed by culprits, and assuming that around 1% of the cards used were to be exploited, this could potentially result in losses amounting to millions of euros in a very short period of time.

Additionally, as already mentioned before, as certain attacks become less expensive, easier to implement or more well-known, the risk associated with it rises significantly, thus causing the overall acceptable risk level to decrease, until adequate countermeasures against such an attack also become common and inexpensive. Nevertheless, a low level of acceptable risk can also act as an incentive for the research, development, implementation or integration of better countermeasures.

Essentially, the current aim of security is rather to make attacks economically infeasible than actually make them completely impossible, based on the level of acceptable risk.<sup>[3]</sup> In this way, a balance between cost and security is created. However, apart from the cost of actual damages or financial losses, security tries to also protect from damages the reputation, brand name and prestige related to the product and its manufacturer, owner or user. Therefore, the level of acceptable risk is also dependent on these matters.

### **Chapter 2:**

# **Background and related work – Optical fault injections and countermeasures against them**

### Optical fault injection

As already mentioned before, fault injection is the process of causing faults and errors in the operation of an integrated circuit. This can be achieved by manipulating data values, or by altering the chip's structure or causing it to generally malfunction, either in a particular point or in its overall function. Different ways and means of injecting faults in integrated circuits have been identified over the years. Some common ways include introducing voltage spikes and clock glitches, making the circuit operate under extreme temperatures, or using radiation, eddy currents or light. [28] However, it has been noted that with all of these ways, except for light, there is no way of controlling the location and the type of fault induced in the circuit.

Considering, in particular, fault injection with the use of light, this is usually performed by lasers, as their beam is quite focused and concentrated, while the spectrum of their wavelength is quite small and narrow. In this way, the effects of this method of fault injection can be isolated within a

specified area and thus the manner in which faults are induced in the chip can be efficiently controlled.

Fault injection can be used for such purposes as retrieving secret information or bypassing secure execution.<sup>[29]</sup> For example, secret keys can be fetched or bypassed by (partial) key nulling, or instructions can be skipped in order to achieve the dumping of memory or to gain access to confidential data.<sup>[4]</sup> Furthermore, the results of induced faults can be used in differential fault analysis in order to extract secret or private data through mathematical analysis.

Optical fault injection is an active and semi-invasive attack on the integrated circuit, [4][7] as it actively intervenes in the chip's operation and the chip needs to be exposed for it to take place. Each chip has a front side, where transistors have been developed and metal layers placed, and a back side which consists of the chip's substrate. As the chip's front side is usually covered in epoxy, if this is not transparent, it has to be removed (a procedure known as decapsulation or decapping) for the attack to take place from that side. [4] Attacks performed from the back side of the chip usually involve depackaging and rebonding the chip, in such a way as to gain access on that side. [4][7]

Optical fault injection can be performed only with a strong source of light, such as a photo flash or a laser beam. However, obviously, a photo flash would not be as accurate and strong as a laser beam, while it may even cost more to acquire an adequate photo flash than to buy a very cheap laser at retail, such as a laser pointer. For these reasons, optical fault inductions tend to be carried out using lasers, while attacks with photo flashes and weak laser beams served mostly as initial proofs of concept. Furthermore, laser fault injection can be performed both from the front and the back side of the chip, but different light wavelengths are needed in order to penetrate each side.

# Specifics of the physical mechanism behind optical fault injection attacks

As optical fault injection was based on the previously observed effects of ionising radiation on semiconductors, <sup>[7]</sup> it makes use of the fact that electromagnetic radiation can temporarily change the state or characteristics of silicon (Si) transistors, causing transient modifications of their functions, which can result in faults and errors in the operation of the overall circuit. <sup>[8]</sup>

Laser fault injection uses light produced by lasers to induce photo-currents<sup>[30]</sup> in the channel region of a transistor, trying to activate that region and cause current to flow through the transistor. Photons excite the electrons in that region of the transistor, therefore creating potential, which in the end results in an induced current between the source and the drain, and, thus, effectively turns the transistor on.<sup>[30][31]</sup>

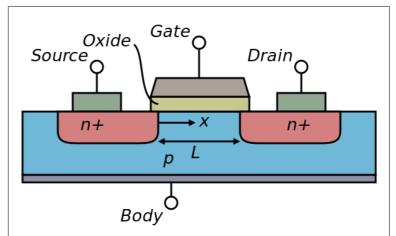

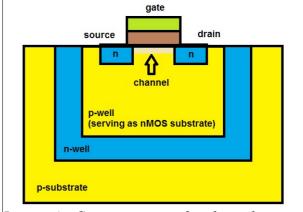

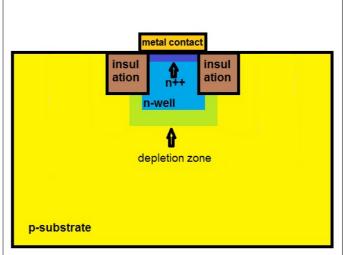

While n-type MOSFETs (Metal-Oxide-Semiconductor Field-Effect Transistors), also referred to as nMOS transistors (image 1), will be turned

Image 1: Cross section of a lateral n-type MOSFET. [32] The channel is formed in the p-doped region of length L between the two n-doped regions, when current runs through it.

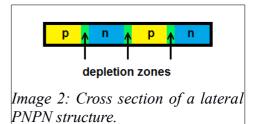

on, in p-type MOSFETs (pMOS transistors) usually only their threshold voltage will be lowered. <sup>[33]</sup> This happens because the activated region of nMOS transistors should have a majority of electrons, while the activated region of pMOS transistors a majority of holes. <sup>[34]</sup> Furthermore, high intensity light over a number of transistors may cause latch-ups; short circuits creating a low-impedance path inside the chip's substrate connecting the low and high power supply rails of a MOSFET circuit, thus trigerring a parasitic structure and disrupting the circuit's operation. <sup>[35]</sup>

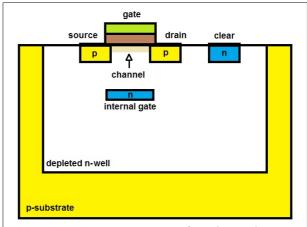

Such parasitic structures behave as PNPN structures (image 2), as they are essentially a pMOS and an nMOS transistor stacked together. Their properties usually resemble those of thyristors, meaning that when one of the transistors is conducting, the other one also starts conducting. The transistors both keep each other in saturation for as long as the structure is forward-biased and some current flows through it. [35]

Given that most chips are today implemented according to CMOS (Complementary Metal-Oxide-Semiconductor) technology, which basically uses complementary and symmetrical pairs of pMOS and nMOS transistors, [36] the above-mentioned difference in the effects of light on pMOS and nMOS transistors should not essentially make a big difference regarding the effects of light on contemporary integrated circuits, where whole specific areas made up by sets of multiple transistors, such as flip-flops, may be targeted.

# Probable targets and technical characteristics of optical fault injection attacks

Flip-flops are probably the most targeted circuits of the whole chip, as they can store information by alternating (flipping) between two discrete stable states and are thus commonly used as memory cells. [37] Furthermore, their internal structure makes it quite easy to change the state of the overall circuit by changing the change of only one or two of their transistors. [7][29][37] Therefore, usually memory circuits and structures are most often targeted by optical fault injection, although other structures related, for example, to the logic of the chip could also be targeted. [38][39]

However, the design and structure of the basic logic circuits are more complex and differ significantly from those of the basic memory circuits. Therefore, it may be much more difficult to successfully make logic circuits perform a desired new operation, different than the one they are intended to perform. Instead, it is more probable that optical fault injection attacks will cause logic circuits to malfunction or cause permanent damage to them or the overall chip. Furthermore, it is improbable that this could be achieved by changing the state of only a few transistors. Nevertheless, faults could be induced optically in logic and, because of the overall structure of the chip, these may be propagated. In this way, after some experimentation, it may be possible to achieve the desired effect of disrupting the chip's operation in an intended and entirely predictable manner, without causing permanent damage. [3][38]

In general, silicon transistors are more vulnerable to optical fault injection with wavelengths between 400 and 700 nm. Wavelengths below 400 nm will be absorbed or reflected, before the photons reach the channel region of the semiconductor, while wavelengths above 700 nm are more likely to pass through the transistor without being absorbed. [40] Furthermore, silicon is transparent to (infrared) light with wavelengths above about 1100 nm. [41]

#### **Technical characteristics of front side attacks**

The front side of a chip usually consists of layers of metal and other shielding material, connecting and protecting the actual transistors which are buried below them and are mostly made of silicon with certain impurities, which enhance silicon as a semiconductor. These intentionally implanted impurities (dopants) in the silicon forming the transistors may make them more vulnerable to light. Depending on the number and kind of layers of metal and on whether the chip is shielded or not, different laser wavelengths may need to be used to successfully attack these transistors. Such laser wavelengths for front side fault injections may range from around 500 nm to around 800 nm, depending on the layers of metal and the shielding. For example, wavelengths of 523, [44][45] 532, [38][46] [47][48] ~650, [7][39] 785, [49] 795[50] and ~800[4][51][52] nm have been used successfully in order to alter the operation of silicon transistors by being shed on their front sides.

Furthermore, unless the chip's covering and the epoxy adhesive used on its front cover are transparent, then these usually need to be removed before a successful front side attack. [4][49] Moreover, increases in the energy and the power of the laser being used will lead to further and/or more successful penetration of the front side of the chip. Depending on the materials of the front side of the side and the wavelength of the laser, some milliwatts may be sufficient for the emitted light to efficiently reach the transistors. [7][39] In other cases, hundreds of milliwatts, or even some watts, may be required. [45][49]

#### **Technical characteristics of backside attacks**

The back side of the chip is mainly composed of the substrate, the slice of silicon on which the transistors were built. In order to penetrate this material and reach the actual transistors, we have to use laser wavelengths for which silicon is semi-transparent, because otherwise most of the light will be absorb by the substrate before it reaches the transistors. These wavelengths are usually between 950<sup>[51]</sup> and 1100 nm, while silicon is transparent for wavelengths above 1100 nm. [41][43][53]

However, not only wavelengths between 950 and 1000 nm have been successfully employed for backside fault injection, [51] but also lower wavelengths of around 800 nm have successfully caused fault injection in chips from their back side. [52] Additionally, after thinning of a chip's back side, laser fault injections with a wavelength of ~900 nm performed on its back side were successful, [54] while thinning the back side can generally provide better results for back side fault injection. [53][55] In general, however, wavelengths above 1000 nm are being used for backside fault injection attacks, with the wavelength of 1064 nm being the most commonly used, [4][53][56][57][58][59][60][61][62][63] along with some cases of a 1065 nm laser also having been successfully employed to induce faults through the back side of the chip. [39][64]

Furthermore, again, increasing the energy and the power of the laser being used leads to further and/or more successful penetration of the back side. Depending on the thickness of the back side and the wavelength of the laser, tens of milliwatts may be sufficient for the emitted light to efficiently reach the transistors. [39][53][57] In other cases, hundreds of milliwatts may be required. [64] Finally, accessing the back side of the chip may require its depackaging and rebonding. [4][7]

### A comparison between frontside and backside attacks

Each side of the chip has different characteristics when a laser beam is shed upon it. The front side can provide a good visibility of the chip's layout, but accurate targeting from that side is difficult

because of its multiple metal layers and potential shielding, which reflect most of the laser's light. [46] Additionally, as technology progresses, the number of metal interconnects on a chip grows, while its size reduces, which makes it even more difficult to reach the transistors of a chip from its front side [46][48]

The back side of the chip does not provide as much visibility of the layout, so positioning is more difficult. [46][48] Furthermore, beams of higher wavelengths than the ones used for penetration of the front side are required in order for the laser light to successfully reach the chip's transistors through its back side. [46][48] However, because of the lack of metal layers and shielding on the back side, the laser beam is not significantly reflected or absorbed before it reaches the chip's transistors and, thus, this attack method is very efficient. [46][48]

### Lasers as a means for optical fault injections

There is a number of reasons why light emitted from laser beams is quite an advantageous technique of inducing faults in an integrated circuit. Among other things, lasers are nowadays pretty cheap and easy to access compared with other material that could induce faults using radiation, such as for example X-ray or gamma-ray emitters. Furthermore, compared with other electromagnetic means, lasers are further more accurate in terms of location than the majority of them, being able to focus on very specific parts of the chip with an accuracy of at most some micrometers, while also being really accurate in terms of timing, as it is possible to select precisely the moment when a laser beam will hit a transistor and for how long this will happen, with an accuracy of nanoseconds. [29] Finally, the faults generated by lasers can be made to last only for the period of time during which the transistor is being hit by the laser beam, in order to cause only temporal faults. [29] In this way, the chip will be completely functional after this period, if some mechanism disabling it after a number of attacks has not been implemented into it, and therefore, the attack will be completely reproducible to its very detail. [29]

However, the laser beam has to be focused on the exact transistor or component that should be attacked, thus the layout of the specific integrated circuit or its relevant region must be known or found out. In addition to this, the time at which the laser beam should hit a transistor and the duration of this must also be specified quite precisely, sometimes with an accuracy of nanoseconds or picoseconds, depending on the chip's internal or external clock and the operation of the overall circuit. Finally, other characteristics of the chip's material, such as silicon's refractive index, must be taken into account when planning an optical fault injection attack. Silicon has a refractive index between 5.6 and 3.5 for wavelengths between 400 and 1100 nm. [65]

Choosing a laser with appropriate wavelength and power to perform an attack is not always easy, as the characteristics of the chip's materials and its layout must all be taken into account. However, as we know the range of wavelengths that are suitable for performing both frontside and backside fault injection attacks with light, we can also pick a laser within those ranges. Additionally, as chips are getting smaller, less energy will be needed to achieve the same results.<sup>[7]</sup> So far, Nd:YAG (neodymium-doped yttrium aluminum garnet; Nd:Y<sub>3</sub>Al<sub>5</sub>O<sub>12</sub>) lasers which produce a wavelength of 1064 nm<sup>[58][59][60][63][66]</sup> seem to be preferred, as their frequency can be doubled to produce a wavelength of 532 nm,<sup>[48][66]</sup> thus being able to perform both frontside and backside attacks. Other lasers with such characteristics would include Neodymium-doped yttrium orthovanadate (Nd:YVO<sub>4</sub>) lasers which also emit a wavelength of 1064 nm<sup>[67]</sup> and Neodymium-doped yttrium lithium fluoride (Nd:YLF) lasers with a wavelength of 1047 nm,<sup>[68]</sup> which can provide a wavelength of ~523 nm with frequency doubling.<sup>[44][45][69]</sup> Furthermore, Ti:sapphire lasers (also known as Ti:Al2O3 lasers, titanium-sapphire lasers, or simply Ti:sapphs) are tunable lasers which emit in the

range from 650 to 1100 nanometers<sup>[70]</sup> and have also been used for both frontside and backside laser fault injection attacks.<sup>[51]</sup> Finally, as already mentioned before, diode lasers of 1065 nm have also been successful in causing optical fault injection in transistors.<sup>[39][64]</sup>

### Continuous wave and pulsed lasers as means for optical fault injections

Moreover, continuous wave or pulsed lasers can be used, i.e. lasers which emit a continuous light beam or lasers which emit a beam in the form of pulses of some duration at some repetition rate. <sup>[71]</sup> It has been identified, however, that the continuous wave laser operation is not really appropriate for precisely localised fault injections, as its collateral energy will effectively stimulate the whole region surrounding the spot that the beam hits, all the time that the laser is on, thus potentially creating unintended faults. <sup>[56]</sup> Therefore, it is far more effective to use pulsed lasers, as these can be switched on for a very short time period, when it is required to do so, and thus, minimise any collateral effects to negligible quantities and assuring resolution to the intended spot size. <sup>[56]</sup>

More specifically, pulsed lasers with a pulse duration of some nanoseconds have been widely employed for laser fault injection attacks. [38][45][54][61][62][72][73] However, also continuous wave lasers [53] or pulsed lasers with a much lower pulse duration of some picoseconds, [51][52][57][60][63] or even femtoseconds [50][51] can induce transient faults. The right pulse duration to be used strongly depends on the circuit's clock frequency, while the laser beam must be triggered at the right point of time and last the right amount of time, in order to induce a fault at the right point of time during the circuit's operation. [4] Therefore, some particular event in the operation of the circuit or some signal must be identified to serve as a trigger. [4]

### Two-photon absorption in silicon and its significance as a future attack mechanism

Finally, silicon exhibits two-photon absorption, a process in which two photons are absorbed to excite a single electron. [74][75][76][77][78] The electron is excited from the valance band to the conduction band, resulting in the generation of an electron-hole pair. [74][77][78] However, it does not seem to exhibit higher multi-photon absorption. [79] This property of silicon has led into new forms of laser fault injection attacks, which employ lasers of higher wavelengths, which produce photons of lower energy, and which can be used to induce photo-currents through two-photon absorption in silicon transistors.

As the following formulas apply, regarding a laser beam's energy and wavelength:

$$f = \frac{v}{\lambda}$$

$$f = \frac{E}{h}$$

$$E = \frac{h * v}{\lambda}$$

$$h \approx 6.62606896 * 10^{-34} J * s \approx 4.13566733 * 10^{-15} eV * s$$

where E is energy, f is frequency, v is velocity (speed) and h is Planck's constant, it is easy to understand that 2 photons of 1340 nm will have the energy of a single 670 nm photon. Of course, this is dependent on the medium through which they move and other conditions, such as temperature, which may affect their speeds. However, in general they cause the same electron excitations on silicon that a photon of around 650-700 nm would.

So far, lasers with wavelengths of 1280<sup>[80][81]</sup> and 1340<sup>[53]</sup> nm have been successfully utilised to inject faults in transistors, taking advantage of the two-photon absorption property of silicon. Both lasers beams had an average power of tens of milliwatts, but while the 1340 nm laser was a continuous wave one,<sup>[53]</sup> the 1280 nm one was emitting pulses of light with a duration of 200 femtoseconds.<sup>[80][81]</sup> Such lasers exhibit an extremely precise location accuracy and may be harder to detect as silicon is transparent for these wavelengths.

### The importance of the laser spot size in optical fault injections

In general, because the feature size of the transistors of chips used in smart cards is already quite small and is going to get smaller in the future, there is also an effort to keep the beam of any laser used in optical fault injection attacks as narrow and thin as possible, in order to be able to attack single transistors. For this reason, the laser beam is usually focused with the help of appropriate lenses in order to reach a spot size (beam width or diameter) of some micrometers.

More specifically, lasers used successfully for frontside or backside attacks tend to have a spot size of a few micrometers,  $^{[4][7][29][39][46][47][48][51][60][61][62][76][82]}$  which means that for manufacturing processes with feature sizes smaller than 120 nm, the laser beam may unintentionally excite several adjacent transistors. This happens because light cannot be focused to a perfect point due to the effects of diffraction. However, depending on the circuit that is targeted even larger laser spot sizes of tens or hundreds of micrometers can be be employed successfully to induce faults to the chip, especially when logic circuits are targeted, since most logic gates take up an actual area of 1  $\mu$ m or larger. However, depending on the circuit specially when logic circuits are targeted, since most logic gates take up an actual area of 1  $\mu$ m or larger.

Finally, lasers used in attacks taking advantage of two photon absorption can have significantly better spatial coherence, [53] causing them to exhibit a smaller spot size of a few hundreds of nanometers. [80][81] This could prove really important as current smart cards employ manufacturing processes of 90 nm or below. Furthermore, the laser spot size used in an attack is also related with the intended amplitude distribution and the sensitivity and structural topology of the circuits to be attacked.

Additionally, it has been noted that wavelengths of 1500 to 1600 nm,<sup>[78]</sup> or 1550 nm in particular,<sup>[74]</sup> may have the same effect on silicon and relevant transistors. However, apart from the particular light wavelengths that silicon may be able to absorb, other factors such as potentially overheating the chip's transistors<sup>[53]</sup> or otherwise damaging them may also be limiting the light spectrum range that can be used in optical fault injection attacks. Nevertheless, using laser beams at an angle<sup>[3]</sup> or taking advantage of the diffraction of a laser or of the interference between two laser beams of the same or different wavelengths may provide ways for more novel successful attacks.

## Light detectors as a countermeasure against optical fault injections

Optical fault injection attacks may be countered by technology hardening, or be addressed by countermeasure mechanisms and structures implemented either at the system level or at the circuit level. [82][87] Countermeasures may include the use of extra layers of protection such as various shields, [39][82][88] trying to reduce charge collection at sensitive nodes by using different materials and techniques for the fabrication of transistors, using extra circuits for error detection and correction (EDAC), or constructing specific structures, such as light sensors and photodetectors, which can detect and effectively counter optical fault injections. [3][4][89][82][87][89]

In general, there is a large number of different countermeasures that can be used against optical fault injection attacks and/or other types of fault injection attacks. [3][82][87][89] However, photodetectors, in particular, can play a significant role in detecting attempts to reach and tamper with the chip's transistors by using light, and can therefore be also employed to effectively prevent such attacks from being successful. [3] For this reason, chips manufactured for secure transactions, such as those found on secure smart cards, may often include photodetectors in their internal structure as a countermeasure against optical fault injection attacks.

### Incompatibilities as a restraining factor

However, even though various different structures and mechanisms can be used to detect the presence of light, many of these mechanisms are too large to be implemented within such integrated circuit structures as today's smart card chips and/or can only detect a quite specific spectrum of light wavelengths and energies. Therefore, it is essential to examine which structures and mechanisms can act as photosensors in silicon integrated circuits currently produced for smart cards, which employ manufacturing processes of 90 nm or below and therefore adhere to their manufacturing and fabrication rules and limitations.

It is obvious that semiconductor structures which can act as photodetectors are inherently well-suited for this purpose, while mechanisms based on completely different materials cannot easily be incorporated in the manufacturing process of integrated circuits. Furthermore, it should be also evident that such structures as active-pixel sensors (APSs) and charge-coupled devices (CCDs), which are a whole integrated circuit, system or device on their own, cannot also be integrated in such other chips as integrated circuits for smart cards, due to their size.

Moreover, other devices such as particle detectors, or detectors which are based on chemical or thermal properties, or which operate in specific extreme conditions are effectively excluded from acting as photodetectors in integrated circuits, because they are either too big, cannot be used repeatedly, or their operation will be affected by the heat the integrated circuit emits on its own during its normal operation, or by other properties of the chip. However, devices which are completely vulnerable to light exposure can still be used as one-time detectors, in order to disable, or completely destroy, the chip after an attack has been detected. This way, although the chip will be rendered useless, it will at least be possible to protect confidential information from being compromised.

### **Compatible devices**

Structures and mechanisms which can act as photodetectors and be successfully incorporated near vulnerable elements inside integrated circuits used for smart cards include photodiodes, phototransistors and photoresistors. These structures are basically common diodes and transistors built by such materials and in such ways that they are more sensitive to light, which causes current to flow through them, or in the case of photoresistors, the resistance of the semiconductor to be lowered. They make use of the photovoltaic, photoelectric and photoconductive effects and can be built in minuscule sizes, as quantum dots, thus also taking advantage of quantum mechanical properties.

#### Diodes

Furthermore, Light-Emitting Diodes (LEDs) can also be used as photodetectors, if reverse-biased to act as photodiodes, while the whole integrated circuit can be constructed in such a way as to act like a photovoltaic cell (a.k.a. a solar cell), especially as a quantum dot solar cell. Other structures, based on vacuum tubes, such as photomultipliers and phototubes, even though they would be really effective, are too big to be incorporated in a contemporary integrated circuit. Finally, photodiodes which are highly reverse-biased can take advantage of the avalanche breakdown effect, which allows the photocurrent to be significantly multiplied within the photodiode.

Photodiodes are diodes which can act as photodetectors and generate a current or voltage when their PN junction is illuminated. [91][92][93][94] If an external reverse bias is applied to them, they operate in a photoconductive mode, while if no bias is applied to them, they operate in a photovoltaic mode. [92] [93][94][95] In the photovoltaic mode, a photodiode's dark current, the current flowing through the device when it is not illuminated, is kept at a minimum. [92][93][94] Even though the speed of response is much faster in the photoconductive mode, the dark current is also increased, without an equal increase in the produced photocurrent. [92][93][94][95]

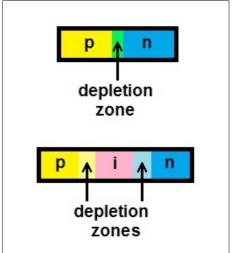

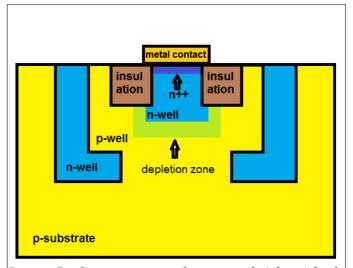

Furthermore, diodes designed to act specifically as photodiodes may use a PIN junction, rather than a p-n junction (image 3), to increase the speed of response and also have a higher detection bandwidth. [93][95] A PIN (or p-i-n) diode contains an intrinsic (i.e. undoped) semiconductor region between the n-doped and p-doped regions of its junction, [96][97]

Image 3: Cross section of a lateral diode with a PN junction (p-n diode) and a lateral diode with a PIN junction (p-i-n diode).

thus having a thicker depletion region. Moreover, photodiodes can be built in such manner as to take advantage of the avalance breakdown effect by being highly reverse-biased. [91][93][97] This causes avalance photodiodes to have a significant internal gain and multiply the induced photocurrents. Avalance photodiodes combine high speed of response with high sensitivity and can be used as silicon photomultipliers. [91][98][99] However, they require a high reverse voltage and their gain (multiplication ratio) is dependent on temperature. [91][99]

Moreover, Single Photon Avalance (photo)Diodes (SPADs) can detect low-intensity light signals down to single photons. [91][99][100][101] They are avalance photodiodes that can provide a much higher gain than normal ones, by being reverse biased with a voltage set higher than their breakdown voltage, [91][99][100][101] the voltage at which the breakdown occurs and an avalance of electrons and/or

holes takes place. This regime of operation is called the "Geiger mode" of use to its analogy to the Geiger-Müller counter. Silicon SPADs can be fabricated with standard CMOS technology, of their dark current must be minimal. However, due to the high voltage used in the reverse biasing of these diodes, their lifetime may decrease significantly, thus making them inappropriate for use

| Material                | Electromagnetic spectrum wavelength range (in nm) |

|-------------------------|---------------------------------------------------|

| Silicon                 | 190 – 1100                                        |

| Indium gallium arsenide | 800 – 2600                                        |

| Germanium               | 400 – 1700                                        |

Table 1: Relation between photodiode material and electromagnetic spectrum wavelength range of detection. [93]

in smart card chips that need to have an extended lifetime.

The spectrum in which a photodiode can sufficiently detect photons is dependent on thematerial that is made of. [93][94][98] Obviously photodiodes made from silicon can detect light in the wavelengths that would excite silicon transistors and flip their state causing a fault, exactly because they are both made pretty much from the same materials (the dopants used in each of them may or may not differ). However, other materials, such as germanium (Ge), indium gallium arsenide (InGaAs), can also detect photons in the electromagnetic wavelength range used in optical fault injection attacks against silicon transistors (Table 1). [93][94][98]

#### **Transistors**

Phototransistors are transistors that are more sensitive to light than usual ones. [93] They are usually NPN bipolar transistors [103] with their reverse-biased base-collector junction being exposed to light, though transparent materials. [93][104][105][106] The photocurrent that is generated in the base-collector junction is injected into the base and amplified by the transistor's current gain. [93] Phototransistors may or may not have a base lead, which would allow their light response to be biased. [103][106] In order to increase their gain even more, they can be more highly reverse-biased, like photodiodes.

Again, the same materials as those used for photodiodes can be used to create a phototransistor, having the same qualities of detection, while there might be a dark current flowing through phototransistors, too. [104][106] The difference between photo transistors and photodiodes is that phototransistors provide much higher gain than the photodiodes, allowing more current to flow when excited by light, and thus also having higher sensivity to light, although they have much slower response times than photodiodes. [93][103][104] If their emitter is left unconnected, they become photodiodes. [93]

Finally, field-effect phototransistors (photoFETs) also exist, being more light-sensitive field-effect transistors (FETs). Unlike bipolar phototransistors, however, they control the drain-source current by creating a gate voltage. Furthermore, there are Darlington phototransistors, which use the standard Darlington transistor configuration with the emitter of the input transistor being connected to the base of the output one and then both their collectors being connected together. The gain of the Darlington transistor pair, which can be used as a single transistor, is the multiple of the gains of the two individual transistors. In the Darling phototransistor (photoDarlington) configuration, the input transistor acts as a photodetector, being a phototransistor. This provides a much higher gain, but the pair is also much slower than an ordinary phototransistor.

One of the differences between the Darlington transistor and a normal one is that the Darling transistor has a higher voltage difference between its overall base and emitter, i.e. between the base

of the input transistor and the emitter of the output one.<sup>[107]</sup> This is also true for the Darlington phototransistor when its base is biased.<sup>[107]</sup>

#### Resistors

Furthermore, photoresistors, also known as Light-Dependent Resistors (LDRs) or photocells, are light-controlled variable resistors, made of high resistance semiconductors, whose resistance depends on light. [109][110] Such materials have a high resistance in the dark, while this decreases in the presence of light. [109][111][112] If the incident light exceeds a certain frequency, photons are absorbed by the semiconductor, producing free electron-hole pairs, which conduct electricity and reduce its resistance. [109][111][112] The more intense the light falling on the photoresistor, the more its resistance will decrease. [110][111]

Photoresistors have a lower sensitivity and higher response times to light changes than phototransistors and photodiodes. Photoresistors also lack a PN junction and act as passive components, in contrast to phototransistors and photodiodes. Furthermore, they exhibit considerable time latency between changes in illumination and changes in their resistance and they may be also sensitive to temperature changes. As they are based on their material's photoconductivity, they may also be called photoconductors.

The most common material used in photoresistors is cadmium sulfide (CdS), [109][111][112] with dopants which may lower the conduction band level. [112] Furthermore, cadmium selenide (CdSe), lead sulfide (PbS), lead selenide (PbSe) and indium antimonide (InSb) are currently used as photoresistors, while also silicon (Si) and germanium (Ge) can also be used as photoresistor materials, especially in components such as Germanium:Copper (Ge:Cu) photoresistors. [109][111][112] The resistance range and sensitivity differ between different materials, with cadmium sulfide and cadmium selenide photoresistors being sensitive in the visible spectral region and lead sulfide, lead selenide and indium antimonide in the infrared, while silicon and germanium are sensitive both in the visible and the infrared spectral regions. [109][111][112][114]

The use of cadmium and lead is severely restricted in the European Union (EU), based on the EU Restriction of Hazardous Substances Directive, and thus the use photoresistors made of lead or cadmium is really limited in the EU.<sup>[109][111]</sup> However, as cadmium sulfide photoresistors are inexpensive and their use has been widespread, the term 'CdS cell' is largely considered synonyms with the term 'photoresistor'.<sup>[112]</sup>

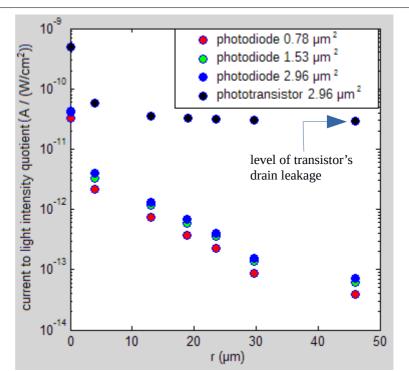

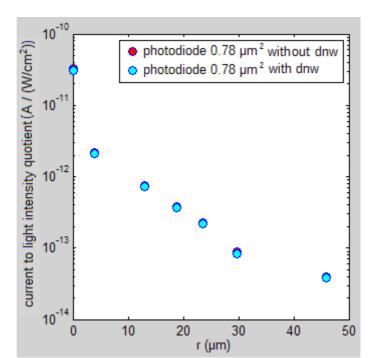

### A comparison of the compatible photodetectors and related potential improvements

It is obvious that different solutions and implementations exist regarding the categories of circuits that can be used as photodetectors in a smart card chip. It is also evident that photodiodes and phototransistors have a few advantages over photoresistors, as they are more sensitive and have a faster response time, with phototransistors being more sensitive, but also having a slower response time than common photodiodes. Furthermore, photodiodes can be reverse-biased by such a high voltage as to be able to detect single photons, while phototransistors in general have a much higher gain than photodiodes.

Moreover, different materials can be used to make a photodetector, such as silicon, germanium or others. It is also quite common for such photodetectors to be incorporated in other structures, including integrated circuits, therefore, their compatibility with chips has already been

demonstrated in the past.<sup>[115][116]</sup> Furthermore, these photodetectors can even be fabricated in miniscule dimensions as nanostructures, <sup>[117][118]</sup> thus their size poses no challenge for integration in the CMOS manufacturing process used for smart card chips today.

Furthermore, it has been noted that common photodiodes have low noise, can be fairly inexpensive, are very efficient and can have a long lifetime. [93] In the future more efficient materials may be used as photodetectors, such as graphene, which has a very wide wavelength range of detection in both the visible and the infrared regions of the electromagnetic spectrum. [119][120] Although graphene, which is a single layer of carbon atoms assembled in a honeycomb lattice, [119] has a very fast response time, it has low sensitivity and no internal gain mechanism of its own. [119][120][121] However, this tends to be improved, [119][120][121][122] especially as graphene is being integrated in the structure of silicon phototransistors or photodiodes, which can provide a high gain mechanism and improved sensitivity. [120][121]

As it has already been demonstrated that graphene photodetectors can be successfully integrated in the CMOS manufacturing process, [120][121][122] it has been suggested that graphene-based integrated electronic-photonic circuits with a wavelength range from 300 nm to beyond 6  $\mu$ m can be expected in the future. [119] Apart from being compatible with CMOS and other relevant technologies, other advantages of graphene are its low cost and the low level of energy required for it to be fully functional in any structure. [120][121]

### The cost of photodetectors in relation to the protection they provide

Of course, there is a need not only to detect an optical fault injection attack, but also prevent such an attack from being successful. To this end, apart from photodetectors, there have to be some dedicated circuits which measure the electrical output of photodetectors and decide whether there has been an optical fault induction attack and which perform some preventive action when such an attack is detected.

It is evident therefore that these circuits need protection from being tampered with, while the whole integrated circuit that incorporates such security circuits needs to be optimised. For this reason, it may be efficient for several photodetectors to share their measurement and response circuits. As these circuits take up an additional area on the chip, they may significantly raise its production costs. However, these issues cannot be easily quantified, because they are strongly dependent on the exact implementation and placement choices made regarding the integration of photodetectors in the chip. Depending on how efficiently this integration is performed, it may or may not be possible to combine or share some of their auxiliary components, which could significantly affect their actual production cost.

Nevertheless, it is true that perfect security does not exist and a balance has to always be maintained between the level of security that a feature provides and its costs, while also taking into account the level of risks and deciding which level of security is really required for a specific chip. [4] Therefore, and as security is defined as a state which is not completely devoid of risk, but which is free of *unacceptable* risk, [123] smart card chips have not only to be protected against the risk of potential compromise, but also be cost-effective, perform well and fail rarely, i.e. be reliable and efficient. [4]

It has therefore been suggested that while photosensors may become really effective in detecting optical attacks and thus preventing them from being successful, it is impossible to really protect each and every transistor and thus an attacker who has found the right position on the chip to attack may still succeed if the laser spot size on the chip is small enough to not trigger the nearest sensor. [4]

For this reason, we will examine the disadvantages, shortcomings and problems of using photodetectors on an integrated circuit and try to come up with potential alternatives, which may not have to replace the use of photodetectors, but can be combined with them or act complimentary towards protecting the chip from optical fault injection attacks.

### Potential problems regarding the operation of light detectors

Photodetectors may have certain limitations regarding their use as a countermeasure against optical fault injection attacks. As already mentioned before, they exhibit certain shortcomings even in their primary function of efficiently detecting the presence of light. In general, their characteristics must be optimised and balance their sensitivity, response time, internal gain and latency, taking into account the associated costs and intended security levels. Again, there is no perfect solution which would maximise their sensitivity and gain while minimising their response time and latency and a compromise must always be made among these characteristics.

As these structures and circuits need to be extremely small in order to fit in miniscule integrated circuits, they also suffer from this trait of theirs, because in order for them to be produced in a small scale, their detection area is also respectively reduced. Furthermore, there are other factors which may affect the effectiveness of using photosensors as a countermeasure against optical attacks such as the threshold voltage needed to signify an attack taking place, which if set too low will cause an unacceptable number of failures and if set too high will fail to detect successful optical injection attempts.

Moreover, photosensors are not always effective on detecting light attacks, as these may happen outside their effective area of detection, or hit the detection area from an inconvenient angle or side. It is important to note here that thinning the material of the chip that the laser beam has to go through before it reaches the chip's transistors can significantly affect the operative area of detection of a photodetector, as the beam will be more focused and there will be less reflection, diffraction and scattering of the beam's photons and thus the detector may not be triggered.

Additionally, refraction, diffraction and interference can be used to guide an attacking beam away from photodetectors. Furthermore, silicon's refractive index increases with optical intensity, because of the electrons and holes that are excited and released, thus exhibiting a Kerr focusing non-linearity. This can cause further issues regarding both the location where photodetectors should be placed to be effective and the characteristics that an attack should have to be successful, such as the beam's angle, intensity and targeted location.

Another important issue regarding photodetectors is that their material(s) may not be equally sensitive along their surface and their reaction may differ depending on the wavelength and angle of the incident photons. Furthermore, design incompatibilities and costs related with the integration of photosensors in the integrated circuits may hinder further their adoption as efficient countermeasures against optical fault injection attacks.

Finally, it is important to note again that since no countermeasure can provide perfect security, it is more reasonable to use a combination of different methods, structures and techniques, both in hardware and software, to protect a chip against any particular kind of attack, than a single type of structure, such as photodetectors. Additionally, despite their potential shortcomings, photosensors can always be improved and enhanced through further development and research, exploring novel structures, approaches and materials. It is therefore essential to examine which alternative solutions can adequately augment photodetectors in providing sufficient security against optical fault injection attacks in smart cards chips. Such protection must not only include the detection of such

attacks, but also ways of neutralising such attempts, for example, by disabling the chip for some time period or locking it indefinitely.

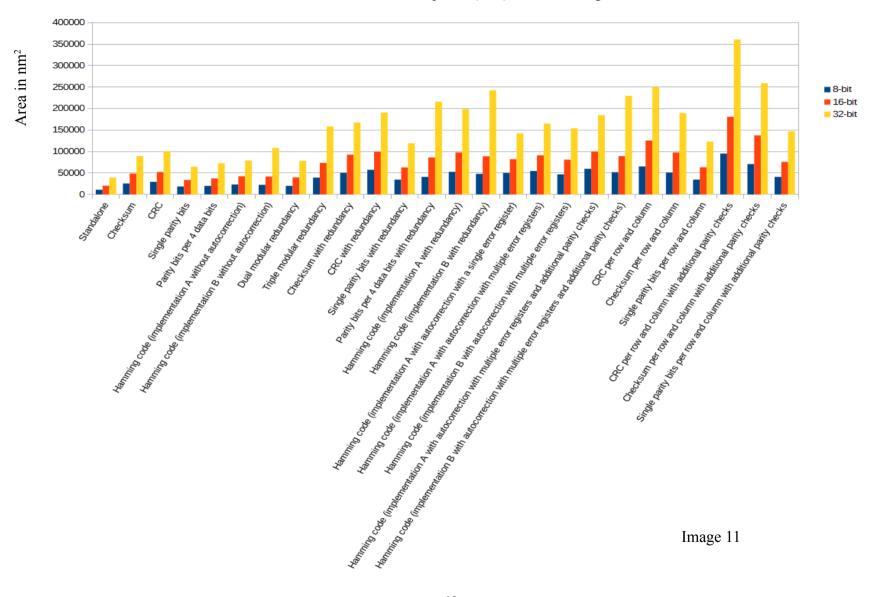

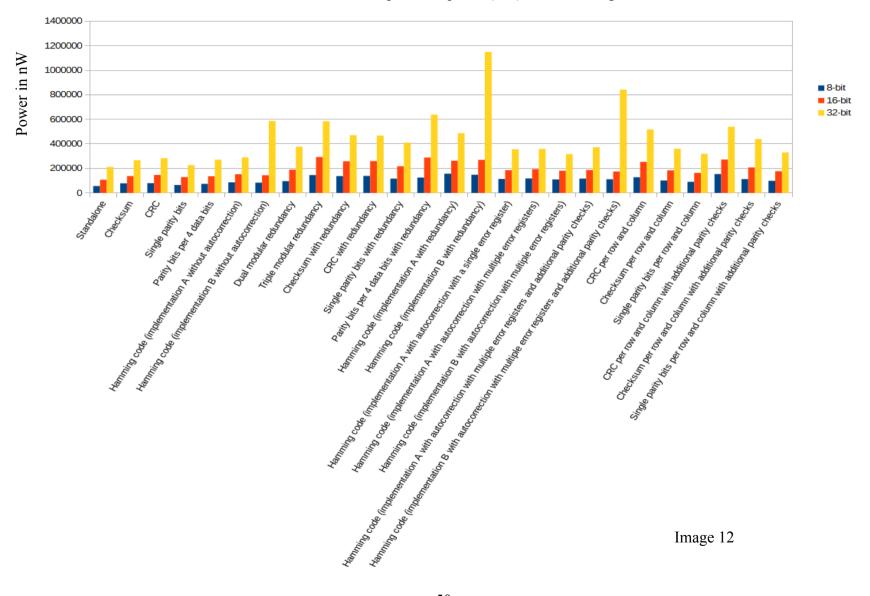

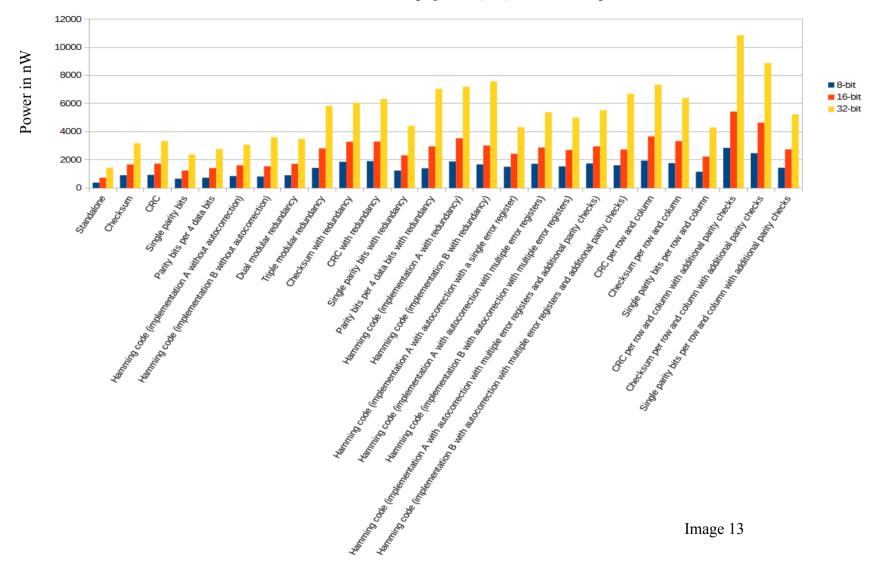

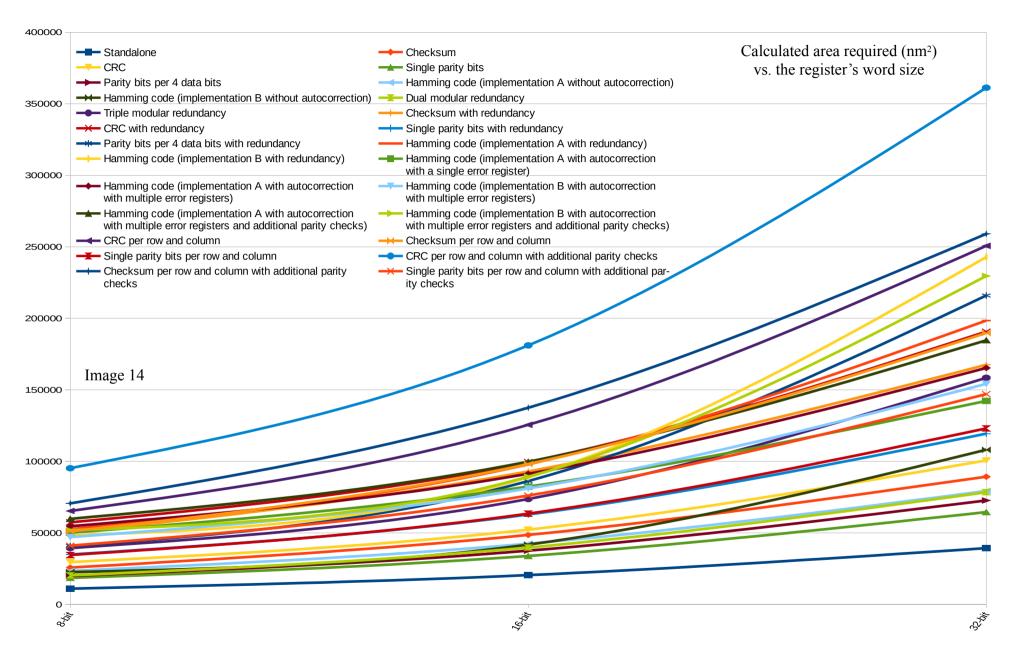

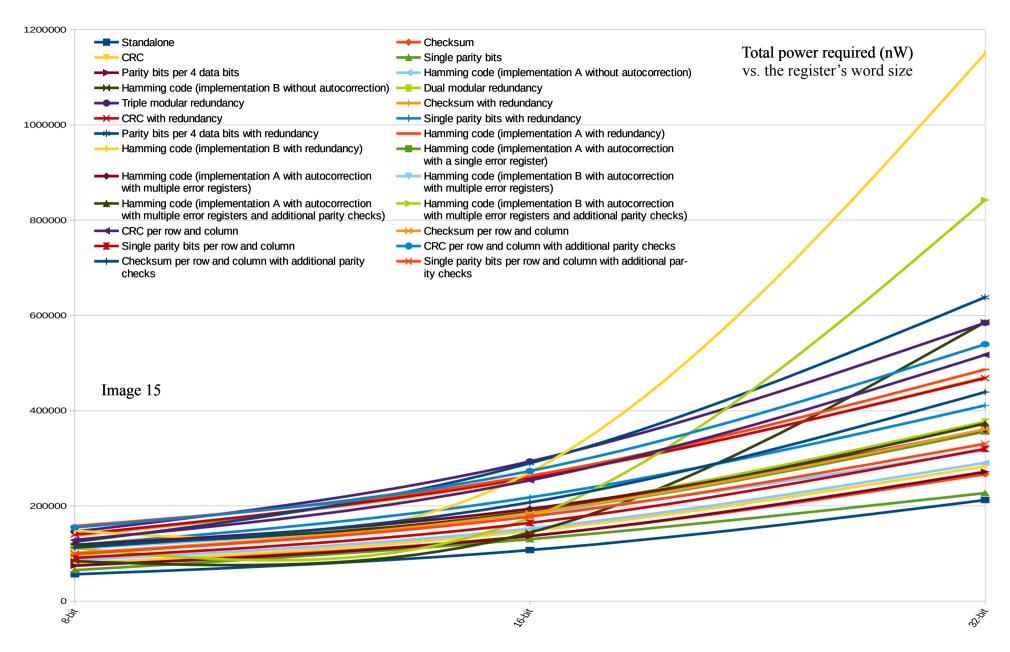

### **Examining possible alternatives**